UART Driver

The UART driver is a char-oriented driver designed to work with a National Semiconductor 16550 UART. The driver is responsible for receiving and sending bytes of data asynchronously. The UART driver still needs work in the area of utilizing the FIFO capabiities of the 16550 UART.

Contents

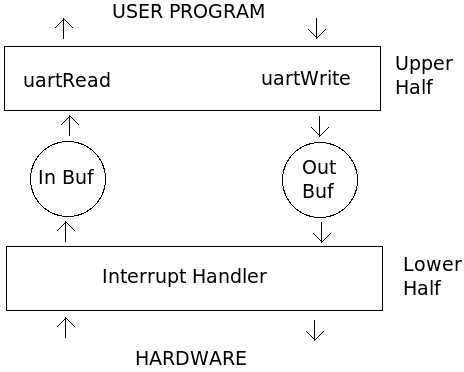

Conceptual structure

The UART driver is divided into two sections: an upper half and a lower half. The two halves communicate via semaphores and buffers.

The lower half is interrupt driven and interacts with the physical hardware. The 16550 UART sends an interrupt (if enabled) when the transmitter is empty or the receiver has a byte. The lower half of the driver handles these interrupts. When data is received, the lower half places the received byte into the input buffer and signals on the input semaphore to make the upper half aware another byte is in the input buffer. When a transmitter empty interrupt occurs, the lower half moves bytes from the output buffer into the transmitter and signals the output semaphore to make the upper half aware another free byte is in the output buffer.

The upper half of the driver interacts with user programs. It does not interact directly with the hardware nor does it spinlock while waiting for the hardware to be ready. The upper half waits on semaphores which are signaled by the lower half to indicate bytes of data or free space are avaialable in the appropriate buffer. Read removes data from the input buffer and places it in a user supplied buffer and returns. Write places data into the output buffer from a user supplied buffer and returns.

Hardware

The following structure represents the hardware control and status registers:

/* Control and status registers for the 16550 UART. */

struct uart_csreg

{

volatile unsigned char uart_buffer; /* receive buffer (read only) & */

/* transmit hold (write only) */

volatile unsigned char uart_ier; /* interrupt enable */

volatile unsigned char uart_iir; /* interrupt ident (read only) */

/* or FIFO control (write only)*/

volatile unsigned char uart_lcr; /* line control */

volatile unsigned char uart_mcr; /* modem control */

volatile unsigned char uart_lsr; /* line status */

volatile unsigned char uart_msr; /* modem status */

volatile unsigned char uart_scr; /* scratch */

};

Some registers are also defined with additional or alternative names for coherent reference.

/* Alternative names for control and status registers */ #define uart_rbr uart_buffer /* receive buffer (read only) */ #define uart_thr uart_buffer /* transmit hold (write only) */ #define uart_fcr uart_iir /* FIFO control (write only) */ #define uart_dll uart_buffer /* divisor latch low byte */ #define uart_dlm uart_ier /* divisor latch high byte */

See National Semiconductor 16550 UART for more details about the hardware.

Control block

The UART driver uses a structure to track all buffers, semaphores, and counts associated with the UART.

/* UART 16550 control block */

struct uart

{

/* Pointers to associated structures */

struct uart_csreg *uart_csr; /* control and status registers */

struct dentry *uart_dev; /* dev structure */

/* Statistical Counts */

int uart_cout; /* characters output */

int uart_cin; /* characters input */

int uart_lserr; /* receiver error count */

int uart_ovrrn; /* characters overrun */

int uart_iirq; /* input IRQ count */

int uart_oirq; /* output IRQ count */

/* UART input fields */

unsigned char uart_iflags; /* Input flags */

SEMAPHORE uart_isema; /* I/0 semaphore for uart input */

unsigned short uart_istart; /* Index of first byte */

unsigned short uart_icount; /* Bytes in buffer */

unsigned char uart_in[UART_IBLEN]; /* Input buffer */

/* UART output fields */

unsigned char uart_oflags; /* Output flags */

SEMAPHORE uart_osema; /* I/0 semaphore for uart output*/

unsigned short uart_ostart; /* Index of first byte */

unsigned short uart_ocount; /* Bytes in buffer */

unsigned char uart_out[UART_OBLEN]; /* Output buffer */

int uart_oidle; /* UART transmitter idle */

};

Functionality

Initialize

/* Initialize structure */ DEVCALL uartInit(struct dentry *pdev)

Intialize defines the starting values for all members of the control block: statistical counts are zeroed, buffers are defined, and semaphores are allocated. Also part of the intialization process is setting values in the control and status registers:

- A baud divisor of 0x000B (11d) is set; assuming x16 clock factor, that gives a base crystal frequency of about 20.275 MHz.

- Line control is set to 8 bit, no parity, 1 stop.

- Receiver FIFO full, transmitt buffer empty, and receiver line status interrupts are enabled.

- Hardware FIFOs are enabled.

Read (Upper Half)

/* Read into user buffer (Upper half) */ DEVCALL uartRead(struct dentry *pdev, unsigned char *buf, int len) /* Read a single character (calls uartRead; Upper Half) */ DEVCALL uartGetChar(struct dentry *pdev)

Write (Upper Half)

/* Write from user buffer (Upper Half) */ DEVCALL uartWrite(struct dentry *pdev, unsigned char *buf, int len) /* Write a signle character (calls uartWrite; Upper Half) */ DEVCALL uartPutChar(struct dentry *pdev, unsigned char ch)

Interrupt Handler (Lower Half)

/* Interrupt handler (Lower Half) */ void uartIntr(void)

Control

/* Control */ DEVCALL uartControl(struct dentry *pdev, int func, unsigned char arg1, unsigned char arg2)

/* uartControl() functions */ #define UART_IOC_SETIFLAG CHAR_IOC_SETIFLAG /* set input flags */ #define UART_IOC_CLRIFLAG CHAR_IOC_CLRIFLAG /* clear input flags */ #define UART_IOC_GETIFLAG CHAR_IOC_GETIFLAG /* get input flags */ #define UART_IOC_SETOFLAG CHAR_IOC_SETOFLAG /* set output flags */ #define UART_IOC_CLROFLAG CHAR_IOC_CLROFLAG /* clear output flags */ #define UART_IOC_GETOFLAG CHAR_IOC_GETOFLAG /* get output flags

/* UART input flags */ #define UART_IFLAG_NOBLOCK CHAR_IFLAG_NOBLOCK /* do non-blocking input */ #define UART_IFLAG_ECHO CHAR_IFLAG_ECHO /* echo input */

/* UART output flags */ #define UART_OFLAG_NOBLOCK CHAR_OFLAG_NOBLOCK /* do non-blocking output */